破坏性电磁兼容性试验案例分析

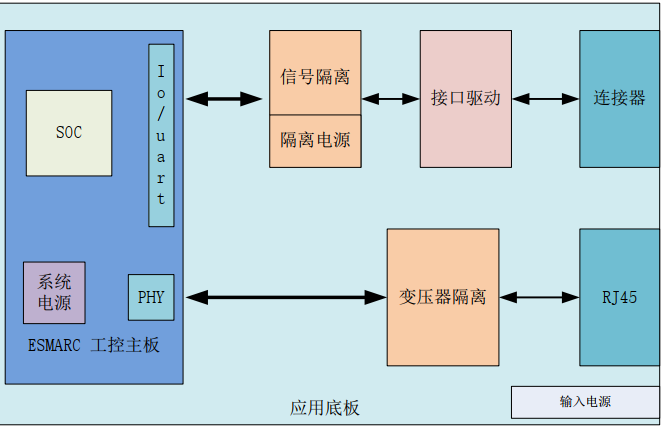

为了协助客户查找电路损坏原因,英创公司特意进行了一系列破坏性的静电抗扰度与浪涌抗扰度试验,以分析电路损坏情况及相关的因素。下图是基于英创工控主板设计的典型嵌入式工控机应用底板的结构,在破坏性试验中,所表现出来的元器件损坏区域,也有针对性。

典型应用底板结构

下面是试验时的几种典型的故障与损坏情况:

| 试验项目 | 故障现象 | 损坏情况 | |||||

| 隔离电源 | 信号隔离 | 输入电源 | 系统电源 | SOC | PHY | ||

| 静电抗扰度试验 | |||||||

| 端口无保护试验 | 死机 | 发烫 | 正常 | 正常 | 正常 | 正常 | |

| 端口保护不合理试验 | 死机 | 损坏 | 损坏 | 正常 | 正常 | 损坏 | 正常 |

| 浪涌抗扰度试验 | |||||||

| 电源端口保护不完善试验 | 死机 | 正常 | 正常 | 损坏 | 正常 | 正常 | 正常 |

| 网络插座接地不合理试验 | 死机 | 正常 | 正常 | 正常 | 损坏 | 损坏 | 损坏 |

| 网络端口差模式试验 | 网络不通 | 正常 | 正常 | 正常 | 正常 | 正常 | 损坏 |

相关破坏性试验的案例更加详细的说明与分析如下:

静电抗扰度 破坏性试验案例

破坏性试验一:端口无保护静电抗扰度试验

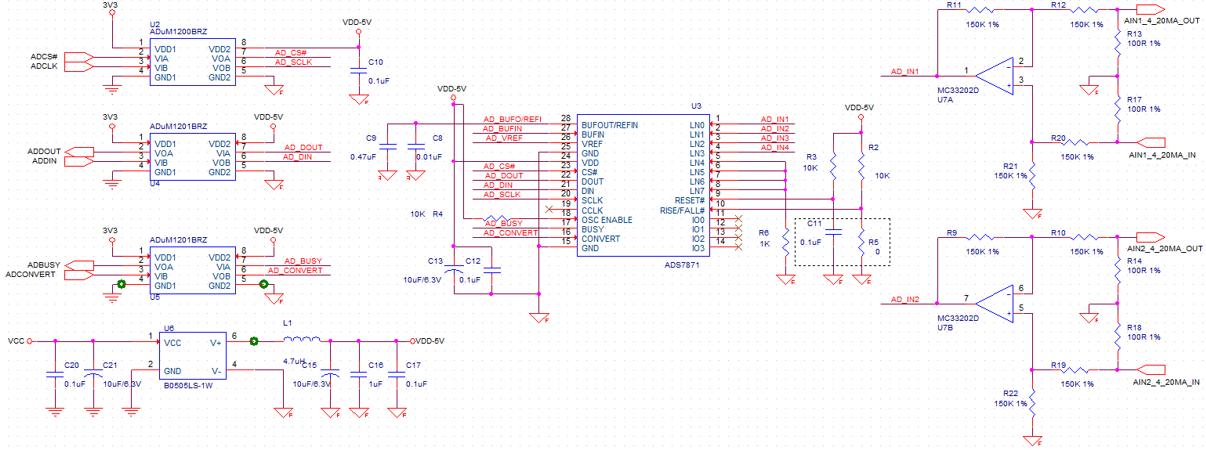

图1:端口无保护的模拟信号输入电路

该试验电路,是4~20mA 模拟输入采集电路,模拟信号输入端口没有设计保护电路,进行静电抗扰度3级(8kV)空气放电实验时, DC-隔离电源U6存在放电火花现象,隔离器件U2、U4、U5件发烫,系统死机。后经检查,电路中并没有元器件损坏,功能正常。试验结果信息如下表所示:

| 区域 | 检修结果 | 说 明 |

| 隔离电源 | 明显放电 | 系统死机,数字隔离器严重发热,且存在明显放电火花现象 |

| 信号隔离 | 发烫 | |

| 输入电源 | 正常 | 试验后进行检查,这部份器件都功能正常,但在实验过程中,存在系统重启现象和系统死机现象 |

| 系统电源 | 正常 | |

| SOC | 正常 | |

| PHY | 正常 |

分析:在试验中,发现系统死机后,并没有继续进行静电放电试验,导致模拟端集累了但又不能击穿隔离器件的电势,因此使信号隔离器件U2、U4、U5发烫,DC-DC隔离电源U6自激,使1、2脚出现短路的现象,最终系统断电,出现系统死机的现象。所以,在后续的检查中,再重新上电,系统又恢复为正常工作状态。但可以肯定,没有元器件损坏,只能算是“幸运”,在这个电路环境下,再进行放电动作,系统中将会有元器件物理损坏。对于这类电路的改进,需要在4~20mA输入端口增加抗浪涌保护器件与抗静电保护器件。

破坏性试验二:RS485端口保护不合理 静电抗扰度试验

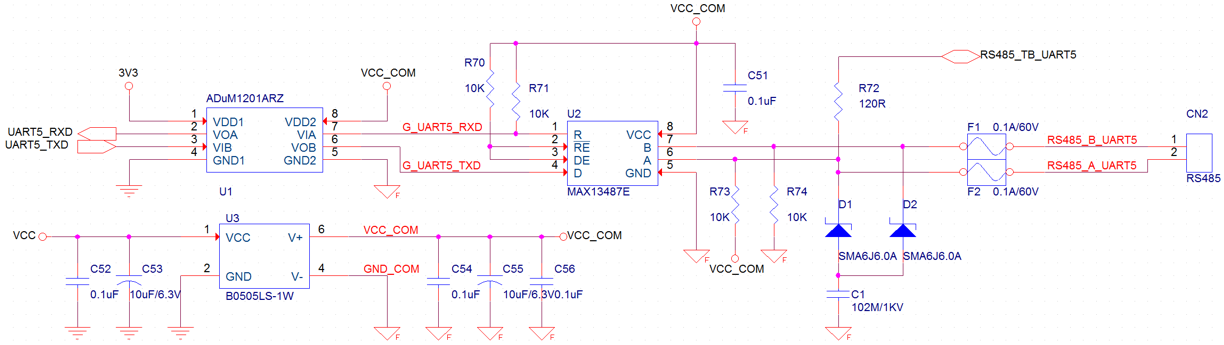

图2:保护电路不合理的RS485端口

上图是RS485端口,它的TVS器件D1、D2下端连接了电容后再到地平面,但没有更有效快速吸收静电的放电回路,因此保护电路设计不合理。静电抗扰度3级(8kV)空气放电试验时,导致RS485通讯相关的数字隔离器件损坏:DC-DC电源U3损坏,数字信号隔离器件U1损坏,同时主板也损坏,CPU发烫,系统无法启动。检查发现,主板3.3V对地短路,最终确认是CPU损坏。试验结果信息如下表所示:

| 区域 | 检修结果 | 说 明 |

| 隔离电源 | 损坏 | 隔离相关器件被烧坏,外表无异常 |

| 信号隔离 | 损坏 | |

| 输入电源 | 正常 | |

| 系统电源 | 正常 | |

| SOC | 损坏 | 由于CPU是整个板卡最脆弱的,因此它更容易损坏。有CPU损坏的板卡,已经没有维修价值 |

| PHY | 正常 |

分析:该电路中,由于D1、D2构成的放电回路经高压电容C1到地平面,会导致静电放电时,电势都积累在电路地平面,最后击穿数字隔离器件U1与DC-DC隔离电源U3,再进一步侵入主板,烧坏CPU的串口资源引脚,使CPU的 3.3V电源脚出现短路的现象。

类似这种情况,英创公司在对客户返回维护的主板中,发现有相当多的现象:IO功能异常,IO损坏,IO对地短路(CPU发烫,电源对地短路),但从外观上又没有明显的物理损坏,那么可以确认,是应用底板的部份端口静电抗扰度特性很差导致。对于这类电路的改进,可参考文档《提高嵌入式设备电磁兼容性的设计参考》中图9进行电路的完善。

浪涌抗扰度 破坏性试验案例

破坏性试验三:电源端口保护不完善 浪涌抗扰度试验

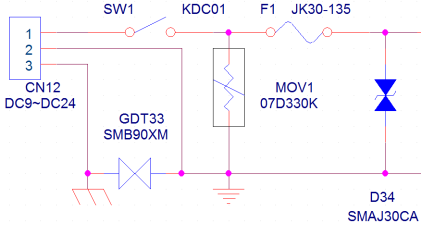

图3:保护电路不合理的DC电源输入端

该电路是直流电源输入端口,在进行浪涌抗扰度 线-线 4级(+/-2kV)试验时,致电源输入端TVS器件D34烧毁短路,系统不启动。试验结果信息如下表所示:

| 区域 | 检修结果 | 说 明 |

| 隔离电源 | 正常 | |

| 信号隔离 | 正常 | |

| 输入电源 | 损坏 | TVS烧坏,裂开并呈短路状态,更换后系统工作正常 |

| 系统电源 | 正常 | |

| SOC | 正常 | |

| PHY | 正常 |

分析:在该电路中,由于电源输入端口抗浪涌保护电路中,差模浪涌脉冲只能利用压敏电阻MOV1和TVS器件D34释放能量,但压敏电阻MOV1反应比TVS器件慢很多,所以D34提前起保护作用。又由于D34能承受的功率有限,因此D34烧坏短路,以致于后面的器件没有再被损坏。在这里,要改善电源输入端的抗浪涌保护特性,需要让功率较大的压敏电阻MOV1启动保护作用,才能释放更大的能量,所以在电源输入线路中,串入了共模线圈,利用电感两端的相位差,使压敏电阻MOV1能比TVS器件D34提前起保护作用,最终达到保护目的。相关的电路,可参考文档《提高嵌入式设备电磁兼容性的设计参考》中图1。

破坏性试验四:网络插座接地不合理 浪涌抗扰度试验

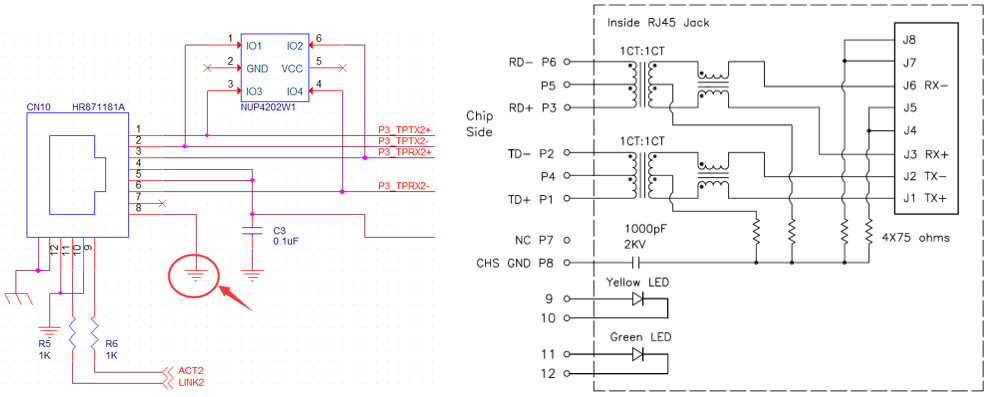

图4:接地错误的RJ45座子 图5:HR871181A内部电路图

在该网络接口电路图中,根据HR871181数据手册,CN10第8脚应该连接到RJ45的金属外壳,并连接到安全接地点,因此这里是不正确的。在进行浪涌抗扰度 线-地 4级(+/-4kV)试验时,能发现CN10金属外壳与系统地平面之间有明显的放电火花现象。在多次放电冲击后,系统死机。后经检查,主板电源芯片,PHY芯片、CPU均损坏。试验结果信息如下表所示:

| 区域 | 检修结果 | 说 明 |

| 隔离电源 | 正常 | |

| 信号隔离 | 正常 | |

| 输入电源 | 正常 | |

| 系统电源 | 损坏 | 主板严重损坏,没有明显外观异常,完全没有维修价值 |

| SOC | 损坏 | |

| PHY | 损坏 |

分析:由于PE端连接错误,即该一体化RJ45座内部电路的第8脚,在浪涌模拟实验时,所有电势能量均进入系统地平面,且没有及时对PE接地点进行放电,使系统地平面电势升高,直接导致系统电源环境错乱,最终损坏大量的低耐压元器件。在英创公司对客户返回维护的板卡中,经常发现主板上存在器件烧裂,或电源烧坏等严重的现象,根据该试验例子分析,可能与设备的PE接地有关:PE接地点错误连接、PE接地不良等。

在对网络端口的进行浪涌抗扰度共模实验过程中总结到一点:由于一体化RJ45连接座的浪涌抗扰度特性有差异,也会对网络端口浪涌抗扰度试验结果产生一定影响。

破坏性试验五:网络端口差模 浪涌抗扰度试验

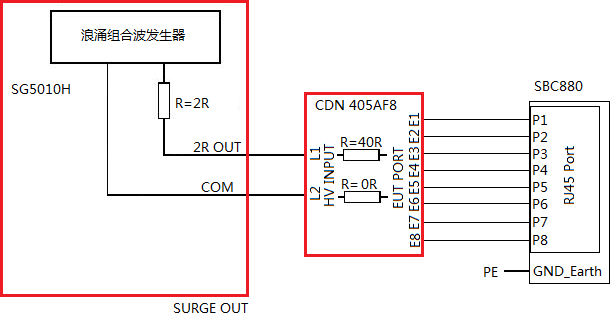

图6:网络端口浪涌抗扰度试验 线-线 耦合示意图

在正常使用环境中,网络通讯线均是双绞通讯线,其特点就是线缆自身就能对降低差模信号的影响。为了验证网络接口在接入浪涌抗扰度 线-线(差模)影响下的情况,特意对网络端口进行浪流抗扰度 线-线 3级(+/-1kV)实验,在SBC880工空机上,采用一体化RJ45连接座HR871181A,会体现出100%导致PHY损坏的情况。试验结果信息如下表所示:

| 区域 | 检修结果 | 说 明 |

| 隔离电源 | 正常 | 网络ping不通,其它功能正常 |

| 信号隔离 | 正常 | |

| 输入电源 | 正常 | |

| 系统电源 | 正常 | |

| SOC | 正常 | |

| PHY | 损坏 | 外观正常,更换后功能正常 |

分析:由于一体化的RJ45座子内部无差模保护相关措施,导致差模信号通过变压器,直接耦合到MDI信号线,同时表现出MDI线上的ESD器件保护无效,最终导致PHY芯片损坏,更换后,功能正常。英创公司的部份客户所返修的主板,就存在PHY芯片损坏比例较大的情况。因此,根据该试验,建议对网线布线环境进行检查,特别是使用了POE的情况。

根据以上对网络接口的浪涌抗扰度试验,需要更进一步提高网络接口的可靠性,可采用分体RJ45连接座(即RJ45插座与网络变压器独立),参考如下电路进行设计,浪涌抗扰度的保护效果会提高:

图7:更完善的分体式网口保护电路

关于更多提高电路静电抗扰度与浪涌抗扰度特性的参考电路,请参考:《提高嵌入式设备电磁兼容性的设计参考》。