在英创工控主板上实现高速工控数据采集

在工业控制领域,数据采集基本上是各类工控智能设备的基础性功能。在很多应用领域,如电力故障录波、电力谐波分析、工程振动冲击监测等,其要求的平均数据采集速率可高达5MB/s(每秒5兆字节)。这样的速率已不可能依靠普通的串行接口,如UART、SPI、CAN来实现。另一方面通过高速的接口如PCIe、USB2.0 / USB3.0来实现高速数据采集,则面临复杂且成本高昂(硬件成本超¥200)的接口电路,因此对成本敏感的嵌入式设备就显得不现实了。

英创公司的主流工控主板产品,如ESM7000、ESM6802、ESM3354等,均配置有精简ISA总线接口,该接口的主要应用之一就是面向工业控制的数据采集。基本的精简ISA总线由8位地址数据总线(分时复用)+ 4条控制信号组成,通过异步操作的读写总线周期,来实现对数据采集单元的控制。精简ISA总线的最大优点硬件接口简单、应用程序接口简单,特别适合在嵌入式系统中使用。但在异步模式下,精简ISA总线的读写速度只能达到4MB/s – 4.2MB/s,还不能完全满足工控领域高速数据采集的需求。

为了满足工控领域高速数据采集的需求,英创公司对其主要的工控主板产品进行了一次升级,为精简ISA总线增加了同步读写功能,使数据读写速度可达到至少12MB/s,同时仍然保持接口电路的简单化。目前支持精简ISA总线高速同步读写功能的主板有:

| 主板型号 | PCB版本号 | 简要说明 |

| ESM7000、ESM7100 | V1.2或以上版本 | 支持ISA总线的同步读写功能 |

| ESM6802 | V2.2或以上版本 | |

| ESM3354、ESM3352 | V4.2或以上版本 |

在常规的异步总线周期中,每个总线周期实现一个字节的读或写操作;而在同步总线周期中,每个总线周期可实现4个字节的读或写,从而使读写速度大幅度提高到12MB/s。对同步读写操作,要求采集数据必须是按4字节倍数提供的。这对具体应用,通常都能很容易就满足这个要求。

支持同步读写模式的精简ISA总线是在基本ISA总线上增加一条总线时钟信号构成的,按ESMARC 评估底板(EVB)的ISA总结接口信号的排序如下:

| 信号及说明 | PIN# | 信号及说明 | |

| RESET_B,硬件复位 | 1 | 2 | ISA_ADVn,地址锁存控制信号 |

| ISA_AD0,地址数据总线,LSB | 3 | 4 | ISA_AD4,地址数据总线 |

| ISA_AD1,地址数据总线 | 5 | 6 | ISA_AD5,地址数据总线 |

| ISA_AD2,地址数据总线 | 7 | 8 | ISA_AD6,地址数据总线 |

| ISA_AD3,地址数据总线 | 9 | 10 | ISA_AD7,地址数据总线,MSB |

| MSLn,支持多模块挂接总线 | 11 | 12 | ISA_WEn,数据写控制信号 |

| GPIO9,可选作为IRQ | 13 | 14 | ISA_RDn,数据读控制信号 |

| GPIO8,可选作为IRQ | 15 | 16 | ISA_CSn,片选控制信号 |

| GPIO25,可选作为IRQ | 17 | 18 | VDD_5V0,+5V供电 |

| GPIO24,作为同步时钟ISA_BCLK | 19 | 20 | GND,电源信号地 |

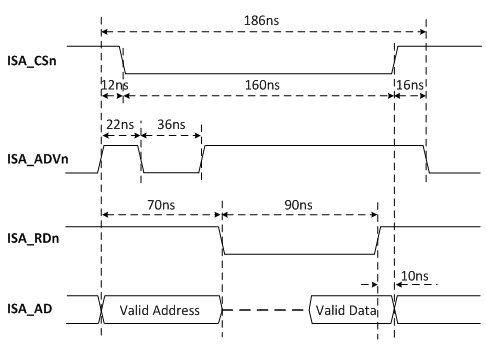

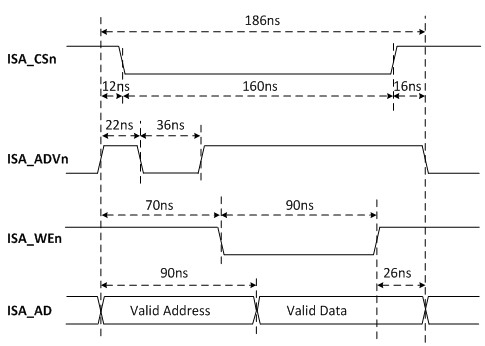

上表列出了8位地址数据总线信号ISA_D0 – ISA_D7,4路总线控制信号(ISA_CSn、ISA_ADVn、ISA_RDn和ISA_WEn)均为低电平有效,对读周期ISA_RDn将有效,对写周期则ISA_WEn有效。基本的ISA总线周期的典型时序如下:

异步读总线时序

异步写总线时序

对异步读写操作,一个完整的读写操作时间包括上述的总线操作周期和总线周期间隔,大约在240ns – 250ns,对应着4MB/s – 4.2MB/s的数据读写速度。

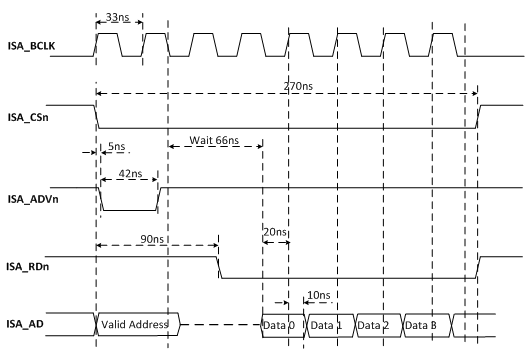

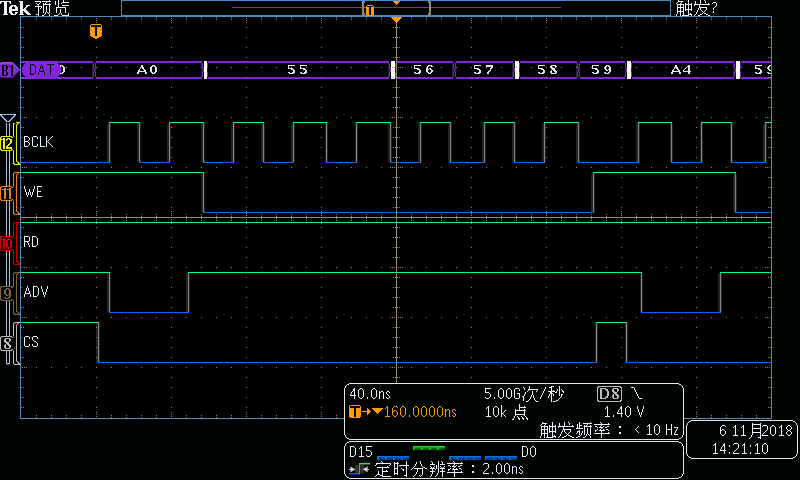

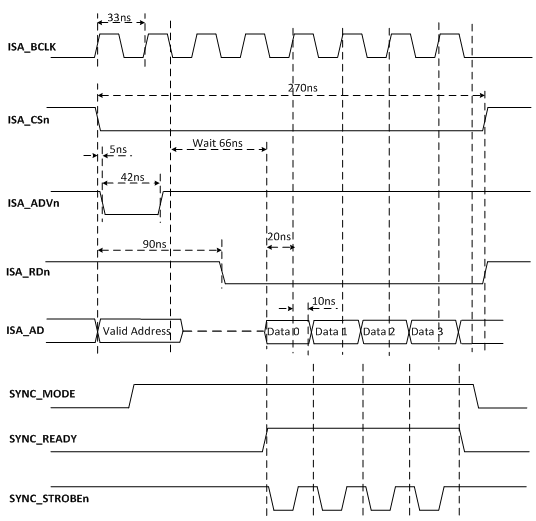

英创工控主板一旦启动ISA总线的同步读写模式,GPIO24管脚将自动切换为总线时钟信号ISA_BCLK,ISA_BCLK仅在总线周期内才有输出脉冲,时钟频率在25MHz – 30MHz。每个总线周期包含8个BCLK时钟,时钟上升沿进行相应操作:第1个BCLK上升沿锁存地址(ISA_ADVn同时为低),之后3个BCLK延时,数据采集单元应在3个BCLK时钟内使数据准备就绪。从第4个BCLK上升沿开始,系统将读取当前数据,同时数据采集单元更新下一个数据至ISA数据总线上。这样循环读4次,总线周期结束。以下是同步读的总线周期时序:

同步读总线时序

同步写总线时序(示波器截屏)

根据上述的总线时序,可以在FPGA或CPLD上用一个简单的状态机,就可译码出锁存更新采集数据的脉冲信号SYNC_STROBE,其上升沿用于更新采集数据。接口电路译码的控制信号如下所示:

同步读总线时序及译码控制信号

在上面的时序图中,信号SYNC_MODE和SYNC_READY由状态机译码产生,SYNC_MODE用于区别读写模式,而SYNC_READY用于生成SYNC_STROBEn:

SYNC_STROBEn = !SYNC_READY | ISA_BCLK;

若BCLK为30MHz,则数据采集单元需要保证在20ns内保证数据在ISA总线上准备就绪,这是对接口电路要求最高的地方。在上述时序中,系统将使用BCLK的第4个至第8个上升沿读取总线上的数据,数采单元将使用SYNC_STROBEn的上升沿更新数据。SYNC_STROBEn的上升沿会比对应的BCLK上升沿延时3-5ns,取决于FPGA或CPLD的门延时。一个完整总线操作过程需要300ns,对应12MB/s的数据读取速度。进一步,还可把一个总线周期的数据读取数从4字节提升至8字节,同时保持译码电路的简洁,这样就可轻松把数据读取速度提升至18MB/s水平。

为了方便客户的应用程序,ISA总线的驱动程序把数据读取长度为32字节的整倍数的情形视为读取采集数据,将自动启动同步读总线模式。其他情况则自动返回异步模式。客户的接口电路,可用SYNC_MODE信号来区别本总线周期的后续是同步操作还是异步操作。下表为精简ISA总线读写速度:

| 总线操作模式 | 数据速率 |

| 异步读 / 异步写 | 4.2MB/s |

| 同步读(4字节) | 12MB/s |

| 同步读(8字节) | 18MB/s |

以上是对精简ISA总线同步读取模式在高速数据采集上的应用简介,有兴趣的客户可与英创公司技术联系,索取更详细的设计资料。技术支持邮箱:support@emtronix.com。